台积电研究大将米玉傑博士透露,台积电将在 2024 年取得 ASML 下世代极紫外光微影设备(high-NA EUV),为客户发展相关的基础设施与架构解决方案。

台积电业务开发副总裁张晓强之前曾经表示,取得设备后,初期主要用于与合作伙伴共同研究。

从之前公布的信息来看,High-NA EUV 光刻设备的单价估计为 4 亿美元(约 28 亿元人民币),是现有 EUV 光刻设备的两三倍。

三星电子副董事长李在镕此前与 ASML 公司就引进该荷兰半导体设备制造商的下一代极紫外(EUV)光刻设备进行了会谈,并就引进今年生产的 EUV 光刻设备和计划于明年推出的高数值孔径(High-NA)EUV 光刻设备达成了协议。

今年早些时候,英特尔还宣布已签署合同购买 5 台这种设备(TWINSCAN NXE:3600D),用于在 2025 年生产 1.8 纳米芯片。台积电也在 6 月 16 日的美国硅谷技术研讨会上表示,它将在 2024 年在全球首次将 High-NA EUV 光刻设备引入其工艺。

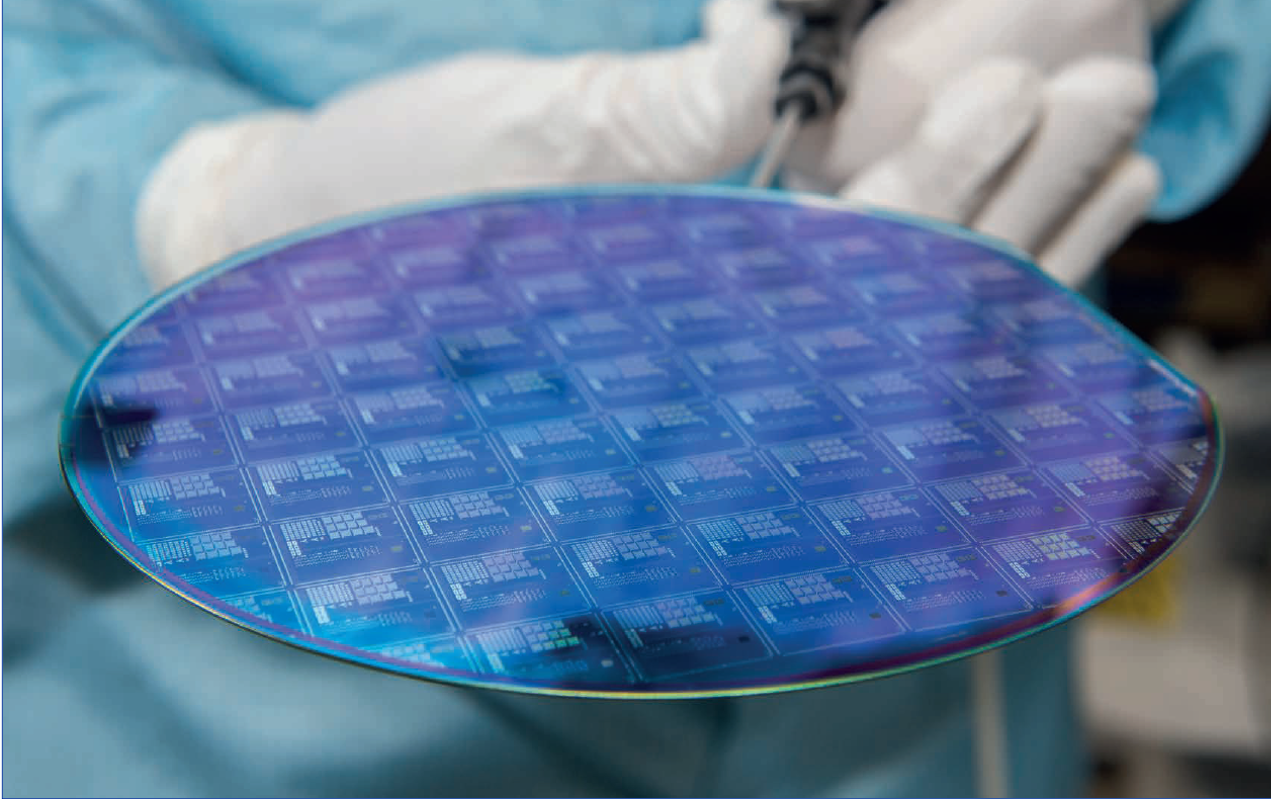

就目前来看,先进光刻技术是衡量芯片制造上限的关键因素,而这种 High-NA 光刻技术有望降低 66% 的尺寸大小。而在芯片制造领域,虽然目前的 3nm、5nm 已经不代表实际栅极宽度,但肯定还是越小越好。

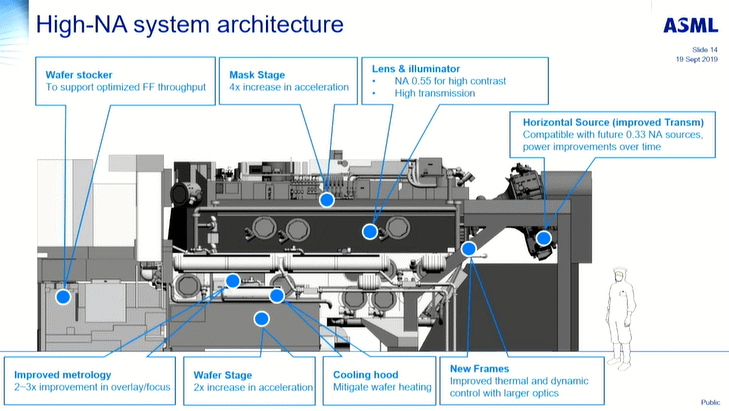

据悉,这款新型 EUV 系统可实现 0.55 数值孔径,与此前配备 0.33 数值孔径透镜的 EUV 系统(TWINSCAN NXE:3400B 和 NXE:3400C)相比,精度会有所提高,可以实现更高分辨率的图案化。

据悉,目前 ASML 每台机器的成本高达 1.6 亿美元,而各大芯片制造商还计划在未来几年投资逾 1000 亿美元建造额外的制造厂,以满足进一步的半导体需求。

官方曾透露,这种 High-NA 机器将比现有机器大 30%,而之前的机器已经大到难以想象,甚至需要三架波音 747 来装载它们。

台积电此前宣布,其目标是在 2025 年量产其 N2 工艺,与 3nm 制程节点不同,2nm 制程节点将使用 Gate-all-around FETs(GAAFET)晶体管,台积电称相比 3nm 工艺会有 10% 到 15% 的性能提升,还可以将功耗降低 25% 到 30%。预计 N2 工艺于 2024 年末将做好风险生产的准备,并在 2025 年末进入大批量生产,客户在 2026 年就能收到首批芯片。