��ý ZDNET Korea ����ʱ����ձ����ƣ����ǵ������ڿ���һ����Ϊ FOWLP-SbS��IT֮��ע��SbS �� Side-by-Side�����ţ����Ƚ���װ������������һ������ Exynos оƬ��ɢ��������

�ִ��ĸ߶��ƶ��˴��������� Exynos 2600��ͨ������ SoC Die ��оƬ�ϼ��ɷ�װ DRAM �ڴ棬�������ߵ�ͬʱ������ռ�������Exynos 2600 ���� SoC Die �������� HPB ɢ�Ƚṹ�������轵���˶�� 16%��

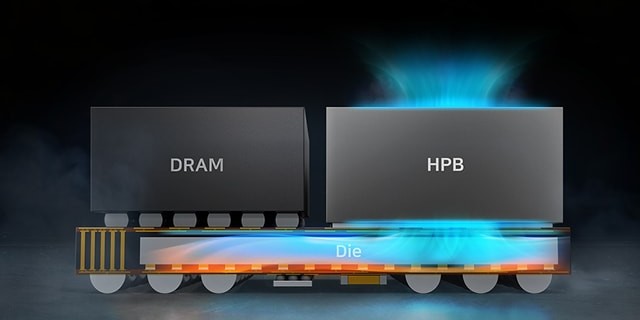

������ Exynos 2600 �ṹʾ��ͼ

���ڲ��� FOWLP-SbS ��װ��оƬ�ϣ�SoC Die �� DRAM ���ŷ��������渲�� HPB���˾����������� SoC Die �� HPB �ĽӴ��������һ����ǿɢ��Ч�ܡ�SoC Die �� DRAM Ԥ�ƽ����û�ϼ��ϼ���ʵ�ֶ̼���Ч������

��ý��Ϊ��FOWLP-SbS �ɽ��ͷ�װ��Ʒ�����֧�ָ���� SoC Die��DRAM�������ڹ�����·������Ż�����Ҳ�������ռ�ø����������Ԥ����������������Ӻ�ȵ��۵�����ƽ��ռ���Գ�����۵�����Ʒ�ϡ�