ОнЭтУН Wccftech ЯћЯЂЃЌЬЈЛ§ЕчНќЦкЙЋВМСЫ CoWoS ЗтзАММЪѕЕФТЗЯпЭМЃЌВЂЙЋВМЕкЮхДњ CoWoS ММЪѕвбОЕУЕНгІгУВЂСПВњЃЌПЩвддкЛљАхЩЯЗтзА 8 ЦЌ HBM2e ИпЫйЛКДцЃЌзмШнСППЩДя 128GBЁЃ

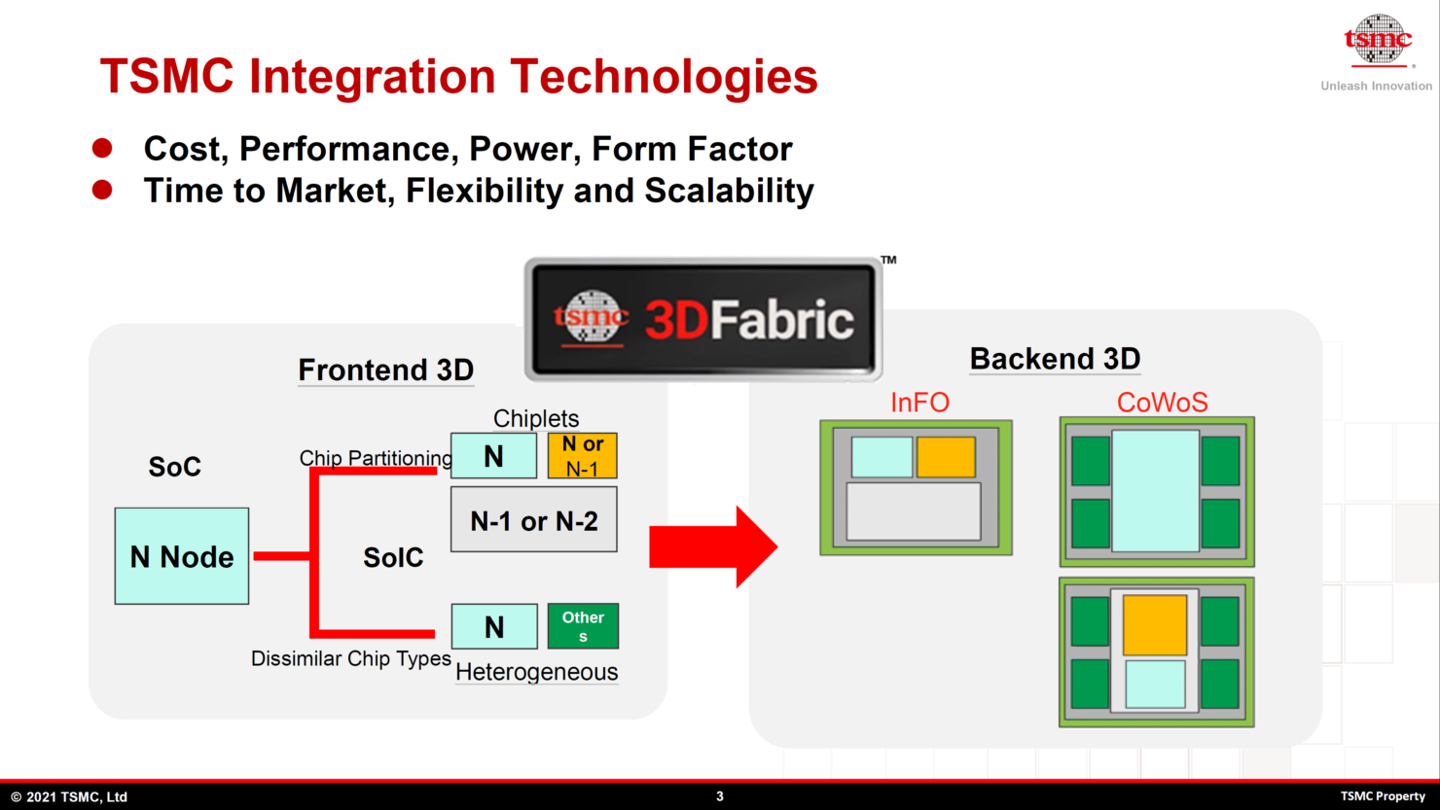

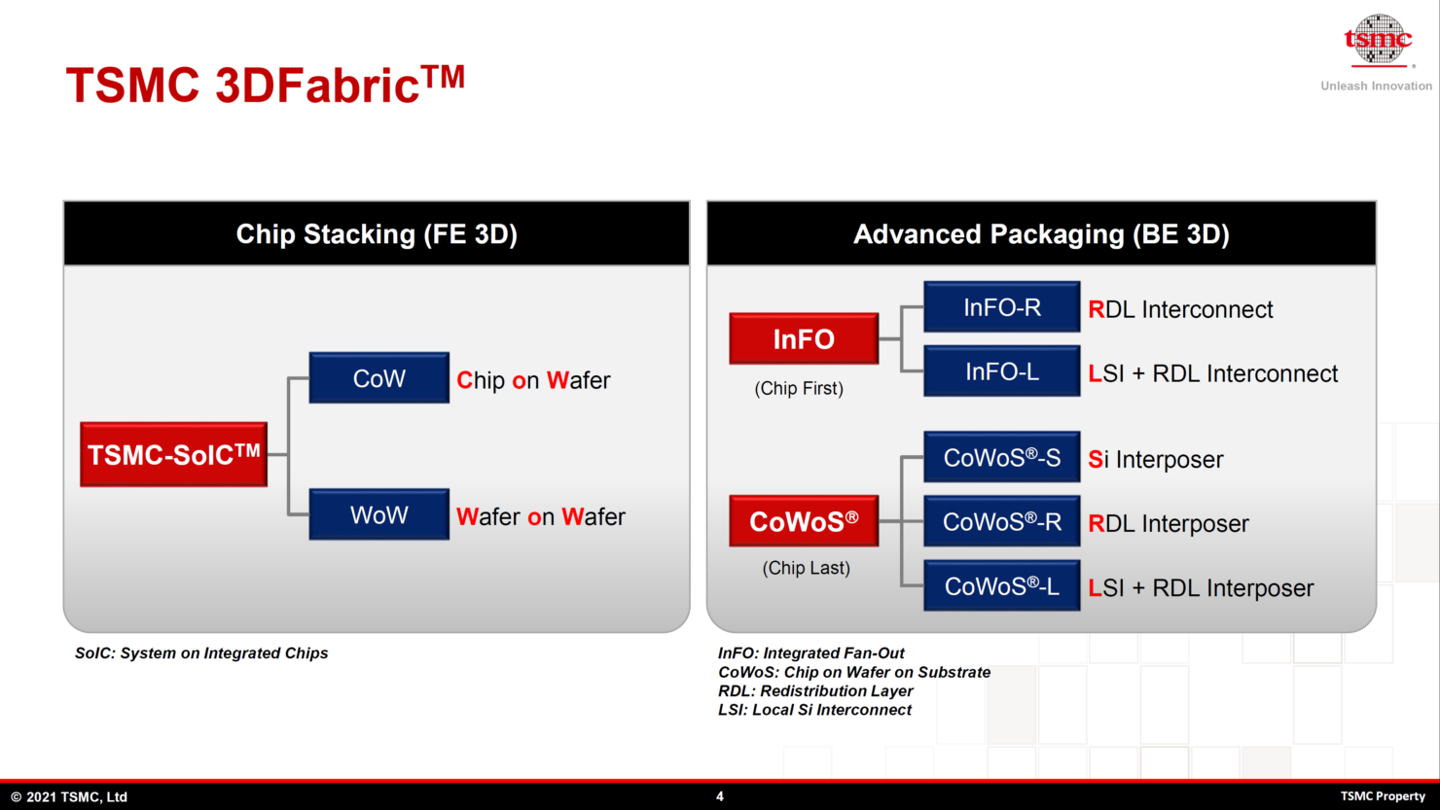

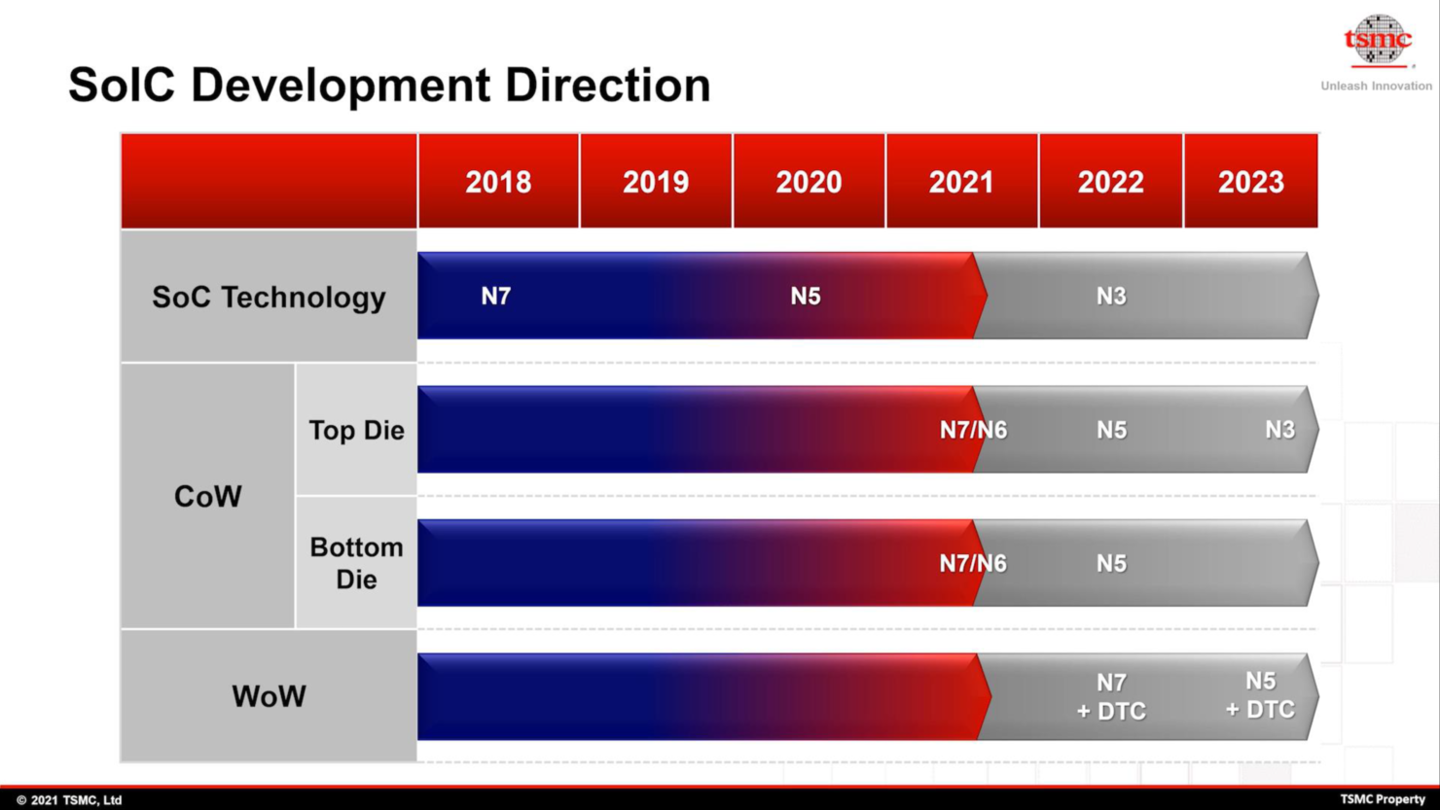

ЬЈЛ§ЕчЕФетЯюММЪѕвбНќЗЂеЙСЫЖрФъЃЌCoWЃЈChip on WaferЃЉ втЮЖзХдкЛљАхЩЯЗтзАЙшаОЦЌЃЛЖј WoWЃЈWafer on WaferЃЉвтЮЖзХдкЛљАхЩЯдйВуЕўвЛЦЌЛљАхЁЃ

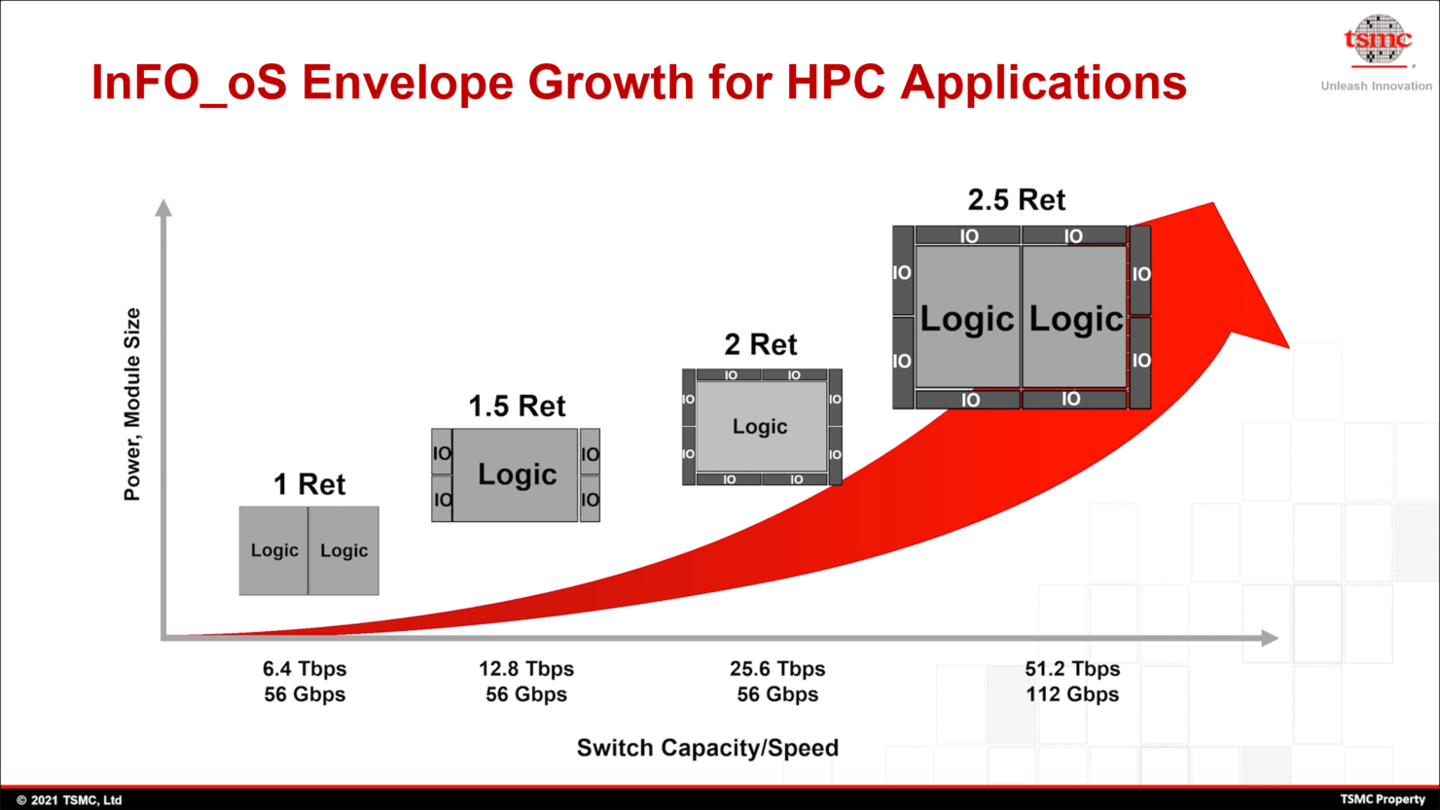

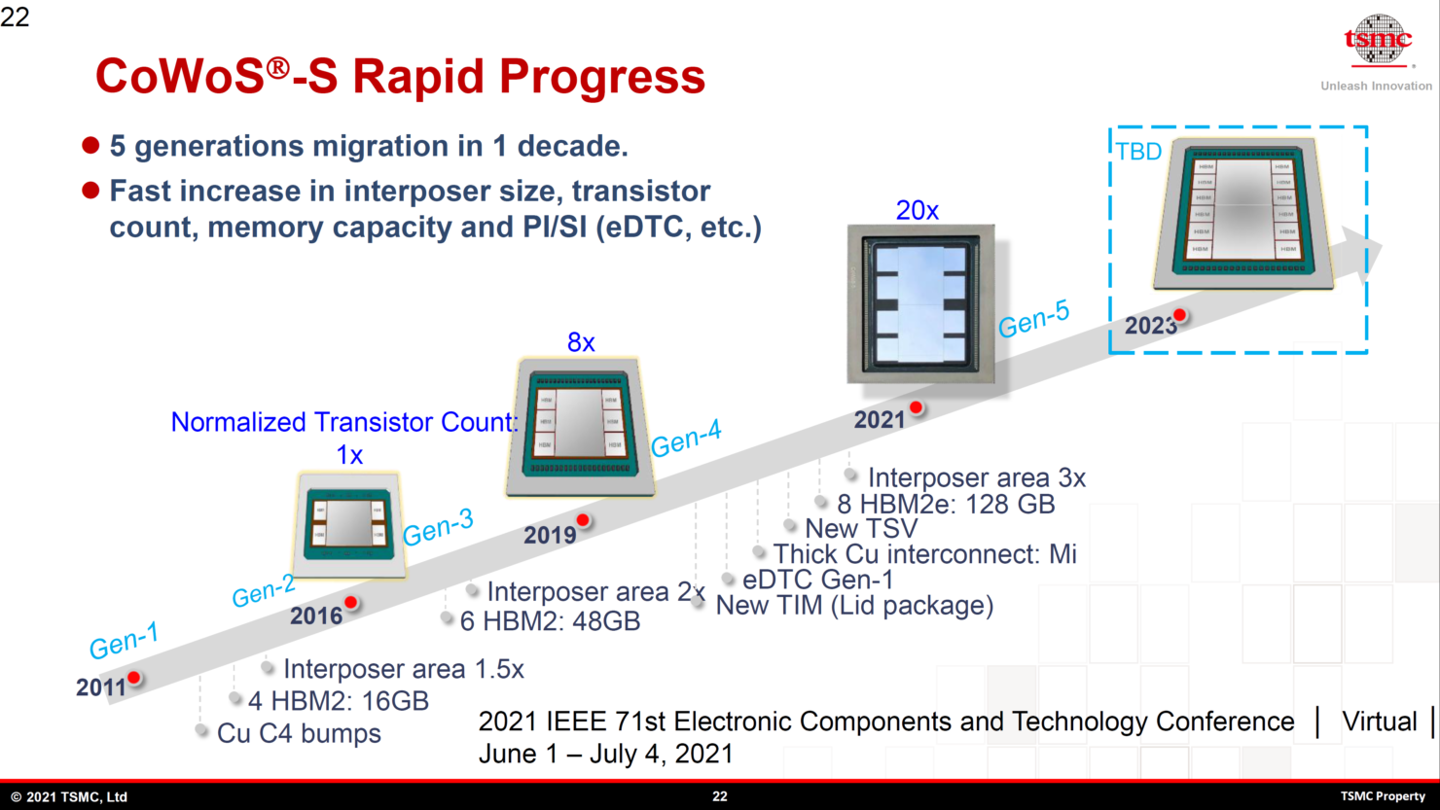

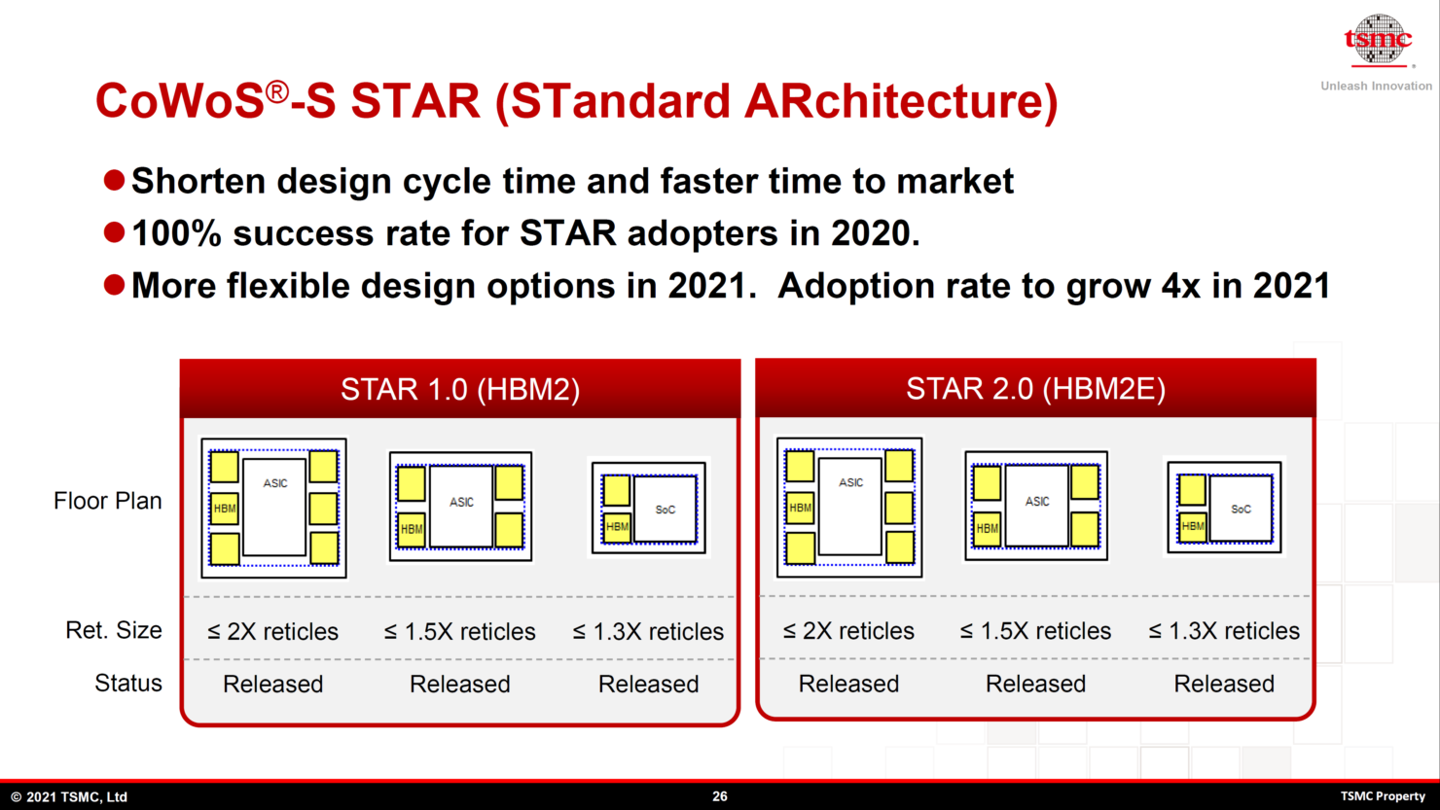

ЙйЗНБэЪОЕк 5 ДњММЪѕЕФОЇЬхЙмЪ§СПЪЧЕк 3 ДњЕФ 20 БЖЁЃаТЕФЗтзАММЪѕдіМгСЫ 3 БЖЕФжаНщВуУцЛ§ЃЌЪЙгУСЫШЋаТЕФ TSV НтОіЗНАИЃЌИќКёЕФЭСЌНгЯпЁЃФПЧАЃЌетЯюММЪѕвбОгУгкжЦдь AMD MI200“Aldebaran”зЈвЕМЦЫуПЈЃЌЦфжаЗтзАСЫ 2 ПХ GPU КЫаФЁЂ8 ЦЌ HBM2e ЛКДцЁЃ

ТЗЯпЭМЯдЪОЃЌЬЈЛ§ЕчЕк 6 Дњ CoWoS ЗтзАММЪѕгаЭћгк 2023 ФъЭЦГіЃЌЦфЭЌбљдкЛљАхЩЯЗтзА 2 ПХдЫЫуКЫаФЃЌЭЌЪБПЩвдАхдиЖрДя 12 ПХ HBM ЛКДцаОЦЌЁЃ

ЬЈЛ§ЕчЛЙБэЪОЃЌаТММЪѕЭЌЪБвВЪЙгУСЫадФмИќКУЕФЕМШШЗНЪНЃЌЕк 5 ДњММЪѕЪЙгУСЫН№ЪєЕМШШВФСЯЃЌШШзшНЕЕЭжСДЫЧАЕФ 0.15 БЖЃЌгажњгкетРрИпадФмаОЦЌЩЂШШЁЃ

ITжЎМвЛёЯЄЃЌAMD дк 7 дТФЉЭИТЖЃЌВЩгУ CDNA 2 МмЙЙЕФ Instinct MI200 Alderbaran МЦЫуПЈвбОГіЛѕВЂНЛИЖЁЃетПюВњЦЗгЕгаЖрДя 256 ИіМЦЫуЕЅдЊЃЈCUЃЉЃЌзмМЦ 16384 ИіСїДІРэЦїЃЌЭЌЪБЛЙОпБИ 16 Иі SE зХЩЋЦїЕЅдЊЁЃ

ЬЈЛ§Еч CoWoS ММЪѕЕФОпЬхЪЕЯжЗНЗЈЃК

вдЯТЮЊЬЈЛ§Еч CoWoS ММЪѕЕФЯъЯИЫЕУїЃК

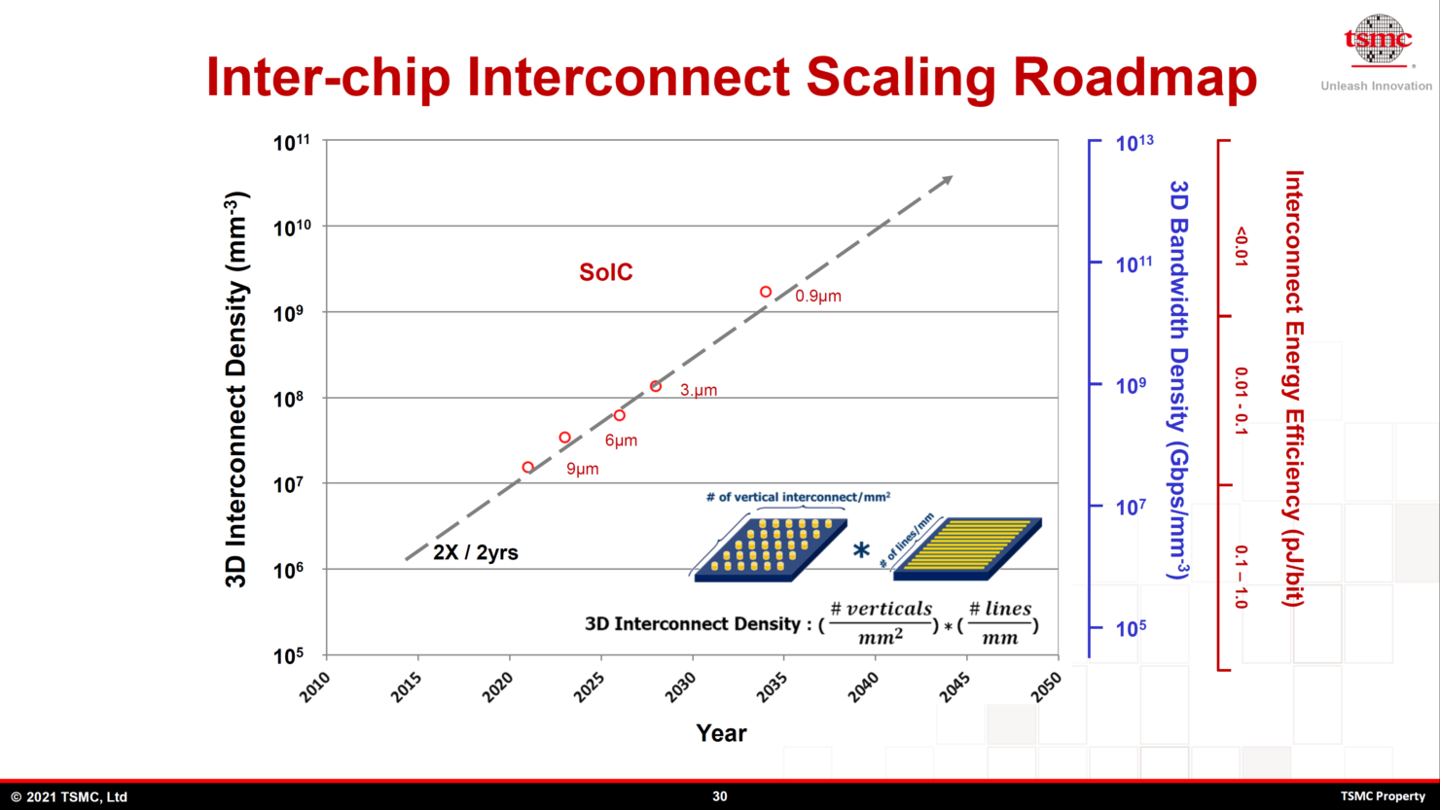

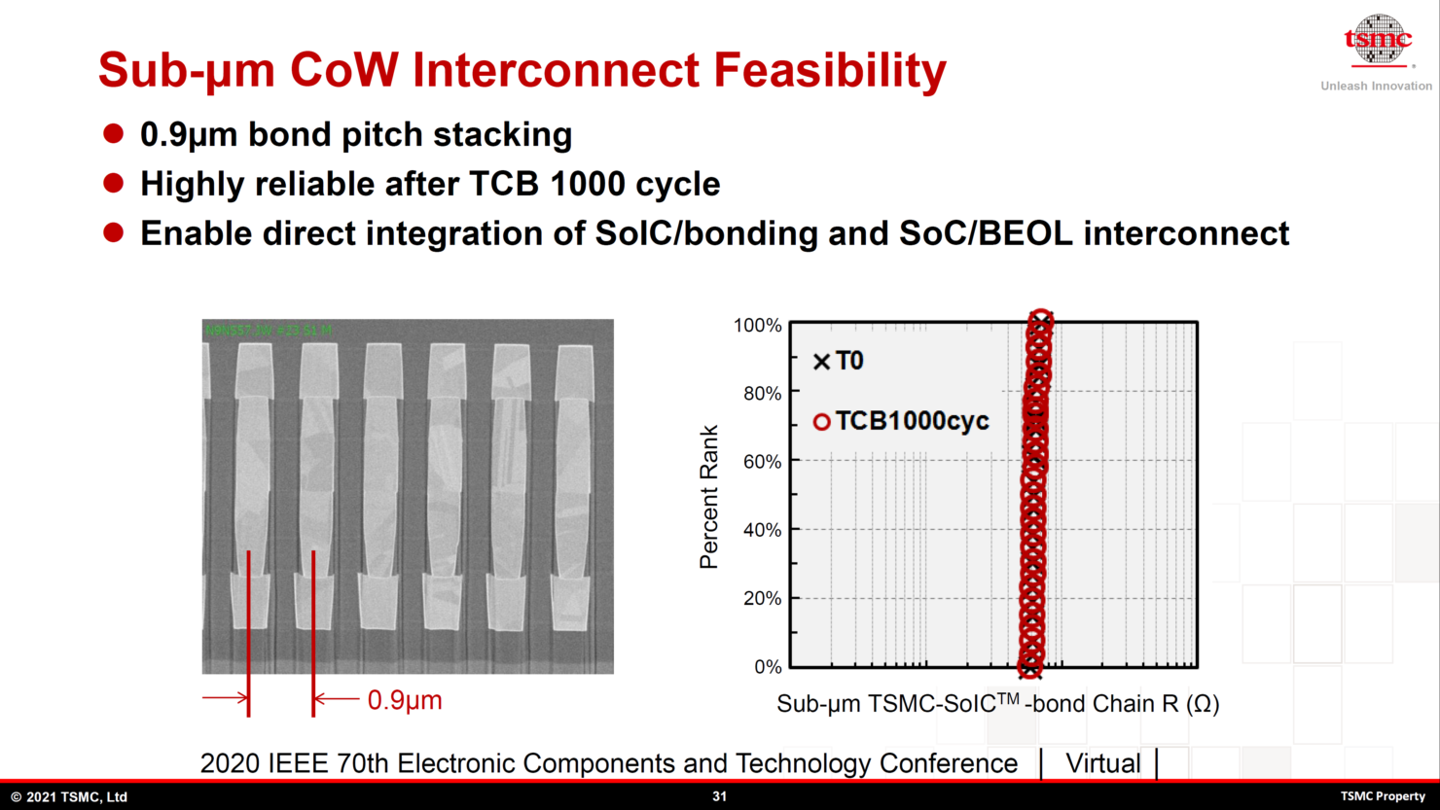

ДгЙйЗНзЪСЯЯдЪОЃЌ2022 ФъНЋЛсЭЦГі 5nmЁЂ3nm жЦГЬЕФаОЦЌЃЌЭЌЪБаОЦЌжЎМфЛЅСЊЕМЯпЕФМфОрвВНЋж№ВНМѕаЁЃЌДг 9 ЮЂУзНЕЕЭжС 0.9 ЮЂУзЃЌдЄМЦдк 2035 ФъжЎЧАЪЕЯжетвЛФПБъЁЃ