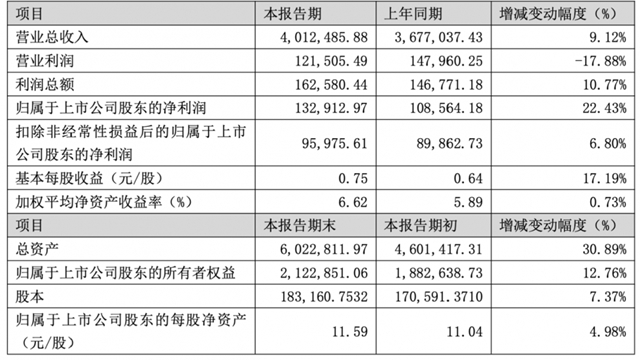

科技媒体 Wccftech 昨日(4 月 13 日)发布博文,报道称面对 AI 产业面临的高级封装产能瓶颈,台积电计划改造 8 英寸晶圆厂并新建设施,预计 2027 年封装产能将从 130 万片提升至 200 万片。

消息称台积电计划布局 7 座先进封装工厂,全面部署 CoWoS、WMCM 及 SoIC 三大核心封装技术。不过高性能计算(HPC)的 AI 芯片需求远超其他细分市场,因此大部分封装产能优先服务 AI 算力基础设施。

产能规划显示,到 2027 年台积电先进封装年产能将从目前的 130 万片晶圆提升至 200 万片,增幅约为 53.85%。

台积电为了快速扩充产能,采取了“新建 + 改造”双轨策略。除了建设新设施,公司还计划将部分老旧的 8 英寸晶圆厂转换为先进封装产线。相比新建工厂,改造现有厂房能缩短设备调试周期,更快响应市场缺口。

与此同时,台积电积极推进在美国亚利桑那州的先进封装布局,两座封装工厂计划于 2030 年投入量产,届时将填补美国本土芯片制造在封装环节的空白。

注:

CoWoS(Chip-on-Wafer-on-Substrate,晶圆上芯片封装)是台积电的核心先进封装技术,将芯片通过硅中介层连接到基板上。

技术原理是逻辑芯片与高带宽内存(HBM)并排放置在硅中介层上,通过微凸块实现高速互连。与传统封装对比,互连密度提升数倍,信号延迟大幅降低,适合 AI 加速器等高性能芯片。

SoIC(System on Integrated Chips,集成芯片系统)是台积电的 3D 封装技术,实现芯片的垂直堆叠。

技术原理是通过铜接合技术将多颗芯片垂直堆叠,无凸块直接互连,间距小于 10 微米。相比 CoWoS 封装技术,SoIC 是垂直堆叠,CoWoS 是水平并排;SoIC 互连密度更高,但散热挑战更大。